CPU的基本组成

PC(Program Counter,程序计数器)

记录当前指令地址Registers(寄存器)

暂时存储CPU计算需要用到的数据。是存取速度最快的

64位CPU就是说该CPU的寄存器一次性能存64位的数字。而ALU和寄存器间也有电路连接,一次性也能读64位

- ALU(Arithmetic & Logic Unit,运算逻辑单元)

JVM :可以当成是Java的模拟计算机

本地变量表:相当于寄存器

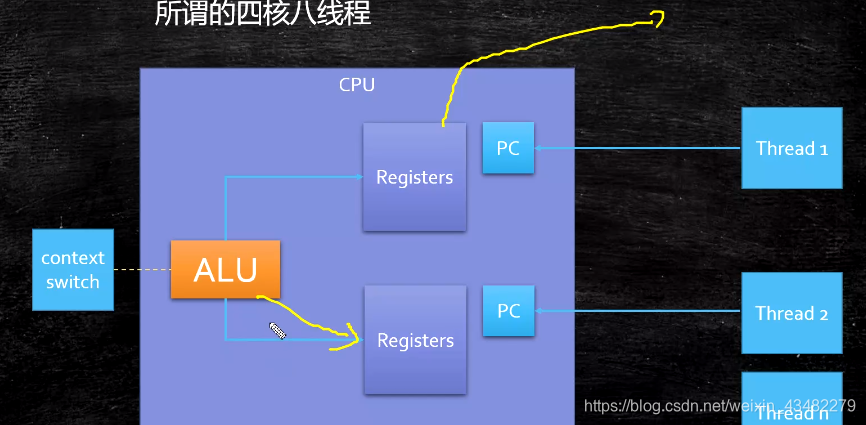

超线程:一个ALU对应多组寄存器|多个PC

线程的上下文切换:把上一个正在运行的线程中寄存器的东西和地址拿出来到缓存,把另一个切换进来。

CU(Control Unit,控制单元)

对中断信号进行控制MMU(Memory Management Unit,内存管理单元)

最早都是软件实现,现在都是软硬件结合实现cache

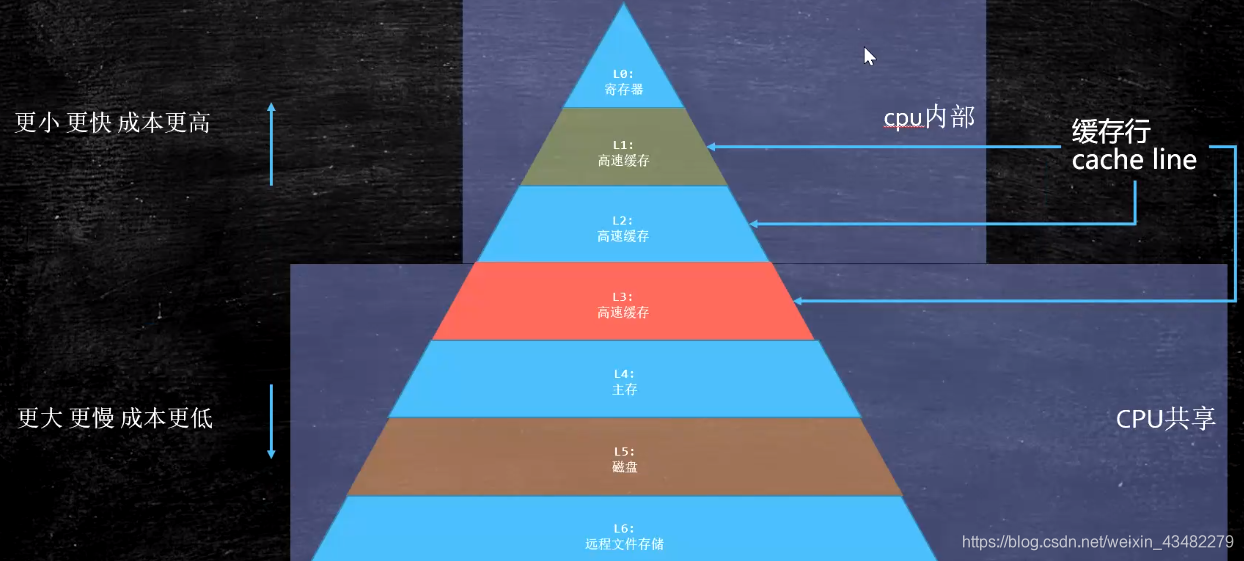

存储器的层次结构

为什么需要cache

缓存物理结构:

按块读取数据

DMA直接发一条指令,直接告诉硬盘把数据装到内存某个位置,硬盘直接与内存打交道。

cache line

Intel中一个缓存行大小为64字节

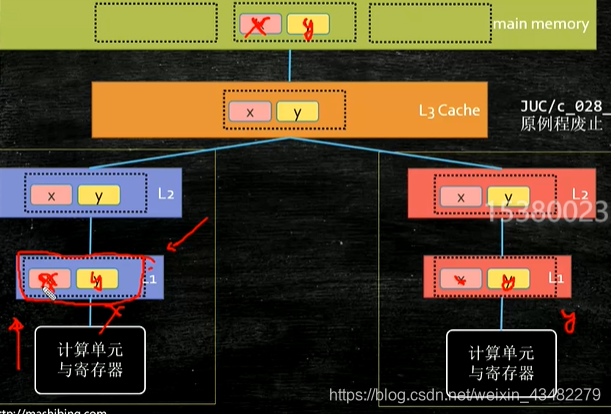

缓存行对齐 **

如果x,y处于一个缓存行。x被修改了,通知其他用到这个行的cpu这个行中数据过期了,执行下一句对y修改的指令时需要重新读一遍。效率非常低。

如果将x,y拆开(位于两个缓存行),效率就会增高。

一个64B的缓存行最多能装8个long。拿空间换时间,保证x,y一定不位于同一行。通知次数减少。

缓存一致性协议不好使时(缓存行装不下,或缓存行数据不允许再往里面装的时候)就要锁总线**。

上锁等情况会强制刷新,其他情况下不一定。

上述可知,两个都需要保持线程一致性,就要保持数据可见性。在这种情况下,两个数字存在一起的时候,反而容易产生伪共享现象,效率反而降低。

伪共享

“我这里改了x通知你,你这里改了y又通知我”的现象。

因此诞生了编程模式。叫做“缓存行对齐”。

对于有些特别敏感的数字,会存在线程高竞争访问。为了保证不发生伪共享,可以使用缓存行对齐的编程方式。

disruptor 框架

是一个并发框架,核心是一个环形 buffer

前面、后面各有七个long,这样无论怎么截取,保证整个缓存行只有它一个数据。

JDK7中,很多采用long padding提高效率

JDK1.8里面,添加了 @Contended 注解,需要加上:JVM -XX:-RestrictContended 可以保证变量不位于同一个缓存行。